uvm验证平台,构建高效芯片验证环境

时间:2024-10-02 来源:网络 人气:

深入解析UVM验证平台:构建高效芯片验证环境

随着集成电路设计复杂度的不断提升,芯片验证在确保设计质量、缩短开发周期中扮演着至关重要的角色。UVM(Universal Verification Methodology)作为一种通用的验证方法学,已经成为业界构建高效芯片验证环境的首选。本文将深入解析UVM验证平台,探讨其构建过程、优势以及在实际应用中的价值。

一、UVM验证平台概述

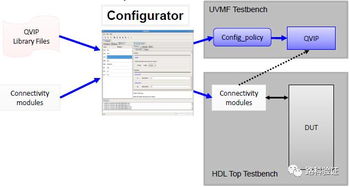

UVM是一种基于SystemVerilog的验证方法学,它提供了一套完整的验证框架,包括验证环境、验证组件和验证流程。UVM验证平台的核心是UVM库,它包含了丰富的验证组件和API,使得验证工程师可以快速构建高效的验证环境。

二、UVM验证平台的构建过程

构建UVM验证平台通常包括以下步骤:

需求分析:明确验证目标,确定验证环境所需的功能和性能指标。

环境搭建:选择合适的开发工具和硬件平台,搭建UVM验证环境。

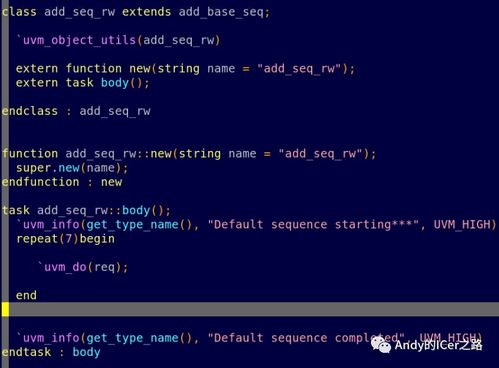

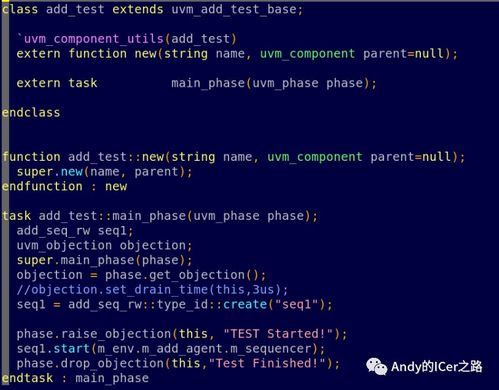

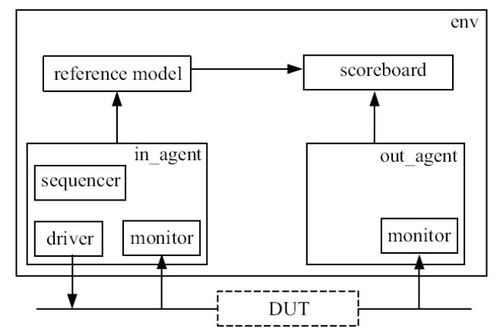

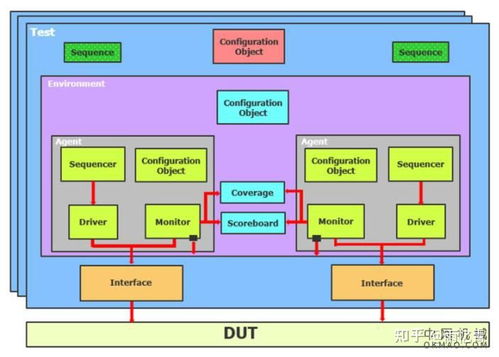

组件开发:根据需求开发验证组件,包括driver、monitor、agent、scoreboard等。

测试用例编写:编写测试用例,模拟实际应用场景,对DUT(Design Under Test)进行验证。

执行验证:运行测试用例,收集验证结果,分析DUT性能。

三、UVM验证平台的优势

UVM验证平台具有以下优势:

可重用性:UVM验证平台采用模块化设计,验证组件可重用于不同项目,提高开发效率。

可扩展性:UVM验证平台支持多种验证方法,可根据实际需求进行扩展。

可维护性:UVM验证平台采用标准化的验证流程,便于维护和升级。

可移植性:UVM验证平台支持多种硬件平台和开发工具,具有良好的可移植性。

四、UVM验证平台在实际应用中的价值

UVM验证平台在芯片设计领域具有广泛的应用价值,主要体现在以下几个方面:

提高验证效率:UVM验证平台采用自动化验证流程,提高验证效率,缩短开发周期。

降低验证成本:UVM验证平台可重用验证组件,降低验证成本。

提升设计质量:UVM验证平台可全面覆盖设计功能,提高设计质量。

促进技术交流:UVM验证平台采用标准化验证流程,促进业界技术交流。

UVM验证平台作为一种高效的芯片验证方法学,在业界得到了广泛应用。通过深入解析UVM验证平台的构建过程、优势以及实际应用价值,有助于验证工程师更好地掌握UVM验证技术,为芯片设计提供有力保障。

相关推荐

教程资讯

教程资讯排行

- 1 vivo安卓系统更换鸿蒙系统,兼容性挑战与注意事项

- 2 安卓系统车机密码是多少,7890、123456等密码详解

- 3 能够结交日本人的软件,盘点热门软件助你跨越国界交流

- 4 oppo刷原生安卓系统,解锁、备份与操作步骤详解

- 5 psp系统升级620,PSP系统升级至6.20官方系统的详细教程

- 6 显卡驱动无法找到兼容的图形硬件,显卡驱动安装时出现“此图形驱动程序无法找到兼容的图形硬件”怎么办?

- 7 国外收音机软件 app,国外收音机软件APP推荐

- 8 Suica安卓系统,便捷交通支付新体验

- 9 dell进不了bios系统,Dell电脑无法进入BIOS系统的常见原因及解决方法

- 10 能玩gta5的云游戏平台,畅享游戏新体验