vhdl硬件描述语言与数字逻辑电路设计第3版

时间:2024-11-26 来源:网络 人气:

深入解析《VHDL硬件描述语言与数字逻辑电路设计》第3版

一、前言

《VHDL硬件描述语言与数字逻辑电路设计》第3版是由我国著名电子工程师张洪波教授所著,该书自出版以来,深受广大电子工程领域读者的喜爱。作为一本经典的教材,该书系统地介绍了VHDL硬件描述语言以及用该语言设计数字逻辑电路和数字系统的方法。本文将对该书进行深入解析,帮助读者更好地理解和掌握VHDL技术。

二、VHDL语言概述

《VHDL硬件描述语言与数字逻辑电路设计》第3版首先对VHDL语言进行了概述,包括VHDL的发展历程、特点和应用领域。VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,用于描述数字电路的行为和结构。它具有以下特点:

支持自顶向下和自底向上的设计方法。

具有良好的可读性和可维护性。

支持多种设计风格,如行为描述、结构描述和数据流描述。

具有丰富的库函数和标准单元。

三、VHDL语言基础

1. 数据类型

数据类型是VHDL语言的基础,包括标准数据类型、用户定义数据类型和数组数据类型。标准数据类型包括整数、实数、布尔值、字符和枚举类型等。

2. 运算符

运算符用于对数据进行操作,包括算术运算符、关系运算符、逻辑运算符和位运算符等。

3. 语句

语句用于描述程序的行为,包括顺序语句、并发语句和过程语句等。

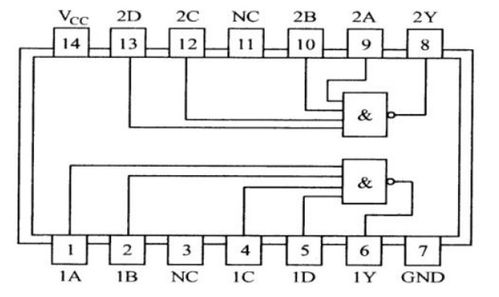

4. 结构体

结构体是VHDL语言中的基本单元,用于描述电路的行为和结构。结构体包括实体、架构和配置等。

5. 库

库是VHDL语言中的函数和过程集合,用于简化设计过程。常见的库包括IEEE标准库、用户自定义库和第三方库等。

四、VHDL设计实例

1. 加法器设计

加法器是数字电路中最基本的运算单元之一。本书介绍了如何使用VHDL语言设计一个4位加法器。

2. 寄存器设计

寄存器是数字电路中的存储单元,用于暂存数据。本书介绍了如何使用VHDL语言设计一个8位寄存器。

3. 状态机设计

状态机是数字电路中的时序逻辑单元,用于实现复杂的控制逻辑。本书介绍了如何使用VHDL语言设计一个简单的状态机。

《VHDL硬件描述语言与数字逻辑电路设计》第3版是一本优秀的教材,它系统地介绍了VHDL语言的基础知识、设计方法和实例。通过学习本书,读者可以掌握VHDL技术,并将其应用于数字电路设计。对于电子工程领域的读者来说,这是一本不可多得的佳作。

相关推荐

教程资讯

教程资讯排行

- 1 能够结交日本人的软件,盘点热门软件助你跨越国界交流

- 2 psp系统升级620,PSP系统升级至6.20官方系统的详细教程

- 3 显卡驱动无法找到兼容的图形硬件,显卡驱动安装时出现“此图形驱动程序无法找到兼容的图形硬件”怎么办?

- 4 能玩gta5的云游戏平台,畅享游戏新体验

- 5 安卓换苹果系统游戏,轻松迁移账号攻略

- 6 oppo刷原生安卓系统,解锁、备份与操作步骤详解

- 7 读书郎平板系统升级,读书郎平板电脑系统升级指南

- 8 国外收音机软件 app,国外收音机软件APP推荐

- 9 海康威视c2c设备不在线,海康威视C2C设备不在线的常见原因及解决方法

- 10 ipad软件老是闪退?,iPad软件老是闪退?原因及解决方法全解析