数字系统设计课程设计,探索FPGA与Verilog的协同应用

时间:2024-09-23 来源:网络 人气:

数字系统设计课程设计:探索FPGA与Verilog的协同应用

随着科技的飞速发展,数字系统设计在各个领域都扮演着至关重要的角色。为了让学生更好地理解和掌握数字系统设计的基本原理和实际应用,许多高校都开设了数字系统设计课程。本文将围绕一个基于FPGA(现场可编程门阵列)和Verilog HDL(硬件描述语言)的课程设计项目展开,探讨其在数字系统设计中的应用。

一、项目背景与目标

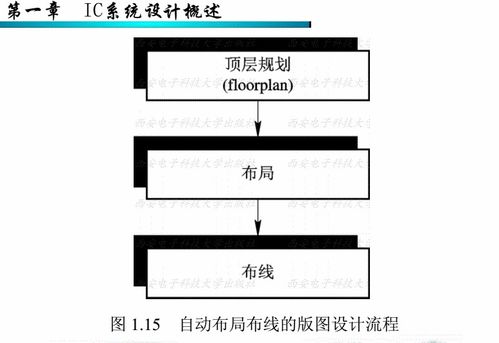

随着集成电路技术的不断发展,FPGA作为一种可编程逻辑器件,在数字系统设计中具有极高的灵活性和可扩展性。Verilog HDL作为一种硬件描述语言,能够将数字电路的设计思想转化为可编程的逻辑代码。本课程设计旨在通过FPGA和Verilog的协同应用,实现一个简单的数字系统设计,让学生深入了解数字系统设计的基本流程和关键技术。

二、项目设计与实现

本课程设计项目以实现一个基于FPGA的数字信号发生器为例,具体包括以下步骤:

1. 需求分析

根据项目需求,确定数字信号发生器的功能,如输出信号类型、频率范围、幅度等。

2. 硬件设计

选择合适的FPGA开发板,如Xilix或Alera系列,并设计相应的电路原理图。根据需求,选择合适的数字信号发生器模块,如正弦波、方波、三角波等。

3. 软件设计

使用Verilog HDL语言编写数字信号发生器的控制代码,实现信号发生器的功能。主要包括以下模块:

时钟模块:产生系统时钟信号。

计数器模块:用于计数和产生信号周期。

信号发生模块:根据计数器的值产生所需的信号类型。

4. 仿真与测试

使用FPGA开发板上的仿真工具,对设计的数字信号发生器进行仿真测试,验证其功能是否满足需求。

三、项目总结与展望

通过本课程设计项目,学生可以深入了解数字系统设计的基本流程和关键技术,掌握FPGA和Verilog HDL的应用。以下是本项目的总结与展望:

1. 总结

(1)通过FPGA和Verilog的协同应用,实现了数字信号发生器的功能。

(2)掌握了数字系统设计的基本流程和关键技术。

(3)提高了学生的实际动手能力和团队协作能力。

2. 展望

(1)进一步优化设计,提高数字信号发生器的性能。

(2)将本项目应用于其他数字系统设计领域,如通信、图像处理等。

(3)探索FPGA和Verilog在人工智能、物联网等新兴领域的应用。

四、结论

数字系统设计课程设计是培养学生实际动手能力和创新思维的重要途径。通过本课程设计项目,学生可以深入了解数字系统设计的基本原理和关键技术,为今后的学习和工作打下坚实基础。随着科技的不断发展,FPGA和Verilog HDL在数字系统设计中的应用将越来越广泛,相信在不久的将来,会有更多优秀的数字系统设计项目涌现。

教程资讯

教程资讯排行

- 1 安卓系统清理后突然卡顿,系统清理后安卓手机卡顿?揭秘解决之道!

- 2 安卓系统车机密码是多少,7890、123456等密码详解

- 3 vivo安卓系统更换鸿蒙系统,兼容性挑战与注意事项

- 4 dell进不了bios系统,Dell电脑无法进入BIOS系统的常见原因及解决方法

- 5 希沃白板安卓系统打不开,希沃白板安卓系统无法打开问题解析

- 6 x9手机是安卓什么系统,搭载Funtouch OS3.0的安卓体验

- 7 安卓系统优学派打不开,安卓系统下优学派无法打开的解决攻略

- 8 安卓车机怎么查系统内存,安卓车机系统内存检测与优化指南

- 9 Suica安卓系统,便捷交通支付新体验

- 10 12pm哪个系统最好,苹果12哪个版本的系统更省电更稳定